DOCUMENTATION 》 TOFFEE with Hardware Compression and Decompression Accelerator Cards

You can build a basic TOFFEE WAN Optimization hardware completely in software layer (i.e its networking data-plane and control-plane). And if you are a product manufacturer you can make commercial WAN Optimization products with TOFFEE with software layer alone. And if you choose to improve its performance, you can use any third-party PCIe Compression Accelerator cards.

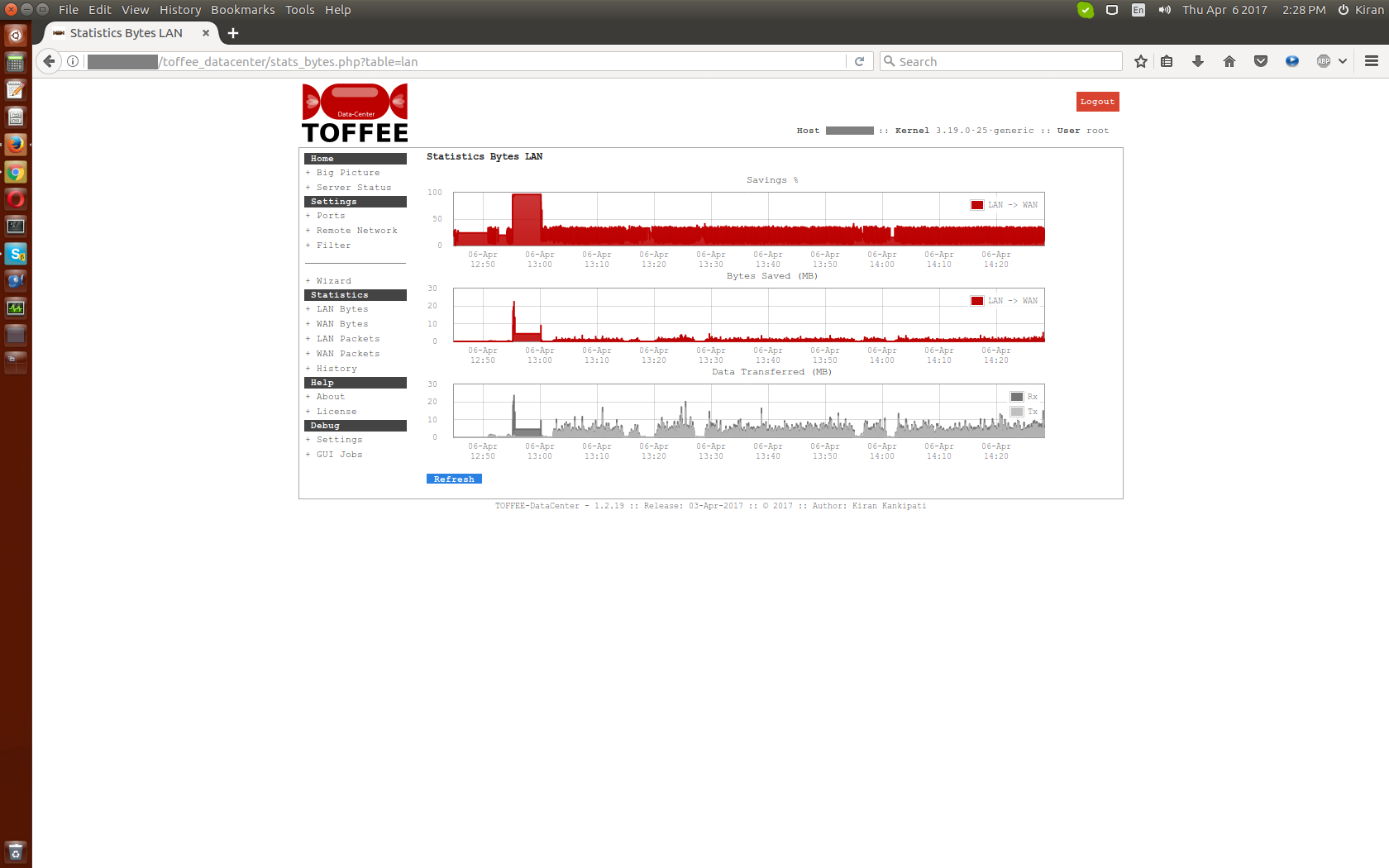

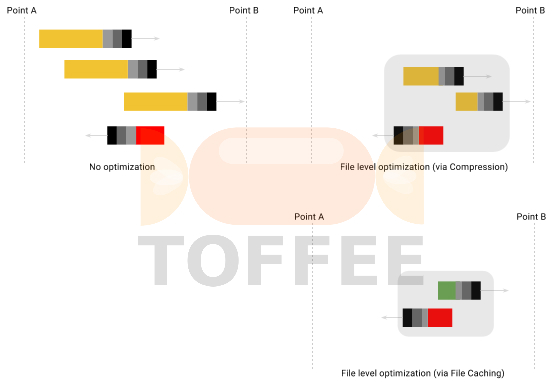

Here is the TOFFEE system architecture with and without hardware accelerator card (i.e Hardware offload). Hardware offload will greatly

reduce the load on general purpose CPU (which is your software/OS layer) and the core data optimization operation such as loss-less

compression (sometimes even encryption) is done within a dedicated Hardware Accelerator card (or chip) as shown below.

![TOFFEE Architecture with Compression and Decompression Accelerator Card [CDN] TOFFEE Architecture with Compression and Decompression Accelerator Card [CDN]](http://sareesaremypassion.org/cdn/the-toffee-project/i/DOCUMENTATION/33/TOFFEE compression hardware.png)

In this case TOFFEE will work as an WAN Optimization framework. With this framework you can architect your entire commercial WAN Optimization product series. You need to modify TOFFEE Linux kernel modules (and APIs) so that it no longer choose kernel's LZ77, LZO or LZ4 software compression libraries (which is CPU bound), instead point to the hardware accelerator card vendor provided kernel's driver/library APIs. This makes packet data compression within TOFFEE Linux Kernel module CPU bound to dedicated co-processor hardware compression accelerator card bound.

It is a well known fact that Linux Kernel's Kernel modules are not great at scaling with multiple CPU Processor Cores. So in a systems architecture point of having more CPU cores in a TOFFEE WAN Optimization device gives no significant advantage. The per-core CPU performance is what required for a workload like TOFFEE packet data optimization. So if architect a high-end WAN Optimization device you need to consider hardware acceleration offload if feasible.

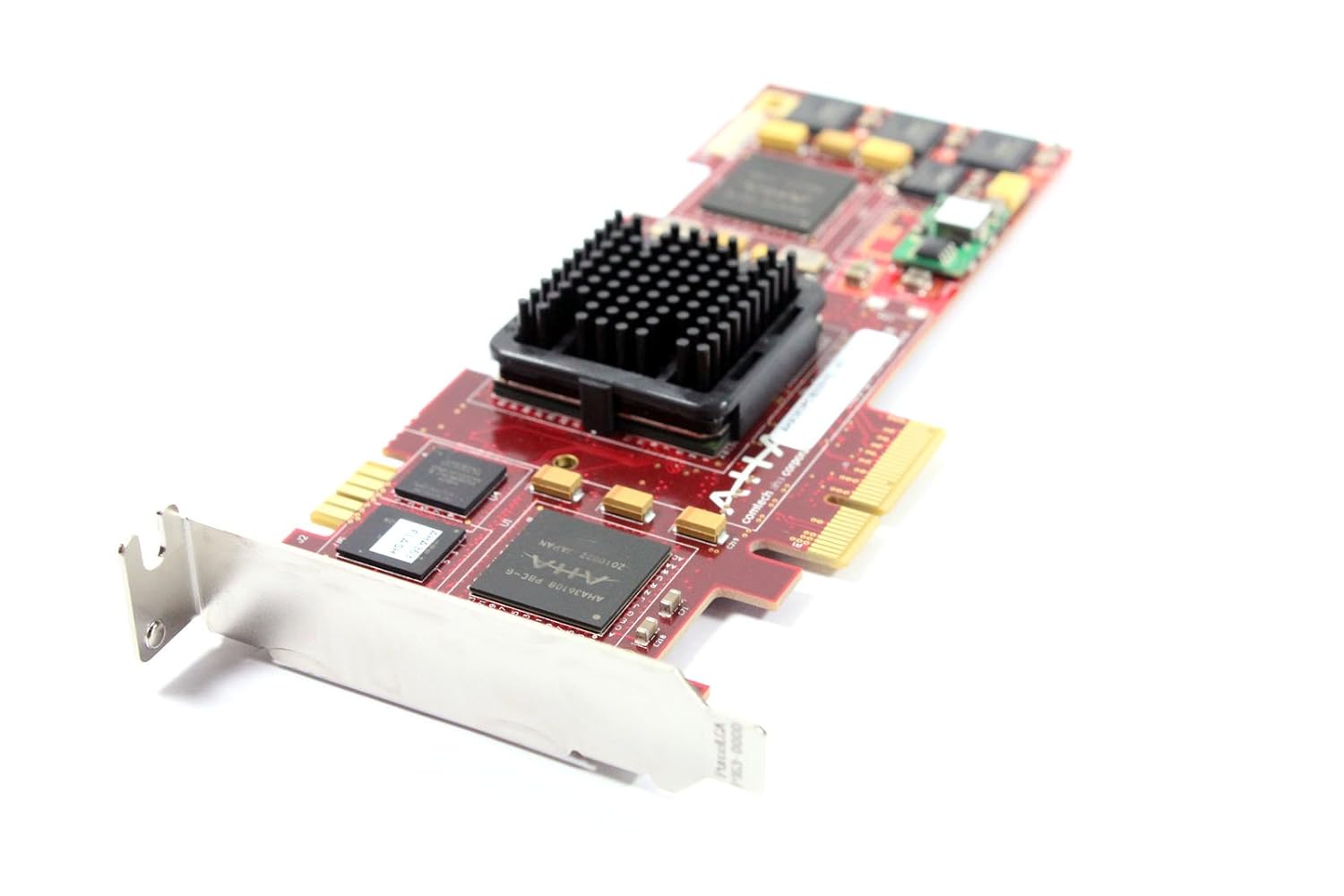

For example: Here is a general purpose AHA AHA363PCIE0301G 5Gbs GZIP Compression/Decompression Accelerator Card.

Typical applications (or use-cases) of this card could be Storage Arrays, Load Balancers, WAN Optimization, Web Servers, Data Analytics, etc.

Image courtesy/link: https://images-na.ssl-images-amazon.com/images/I/61kMl1v4BmL._SL1500_.jpg

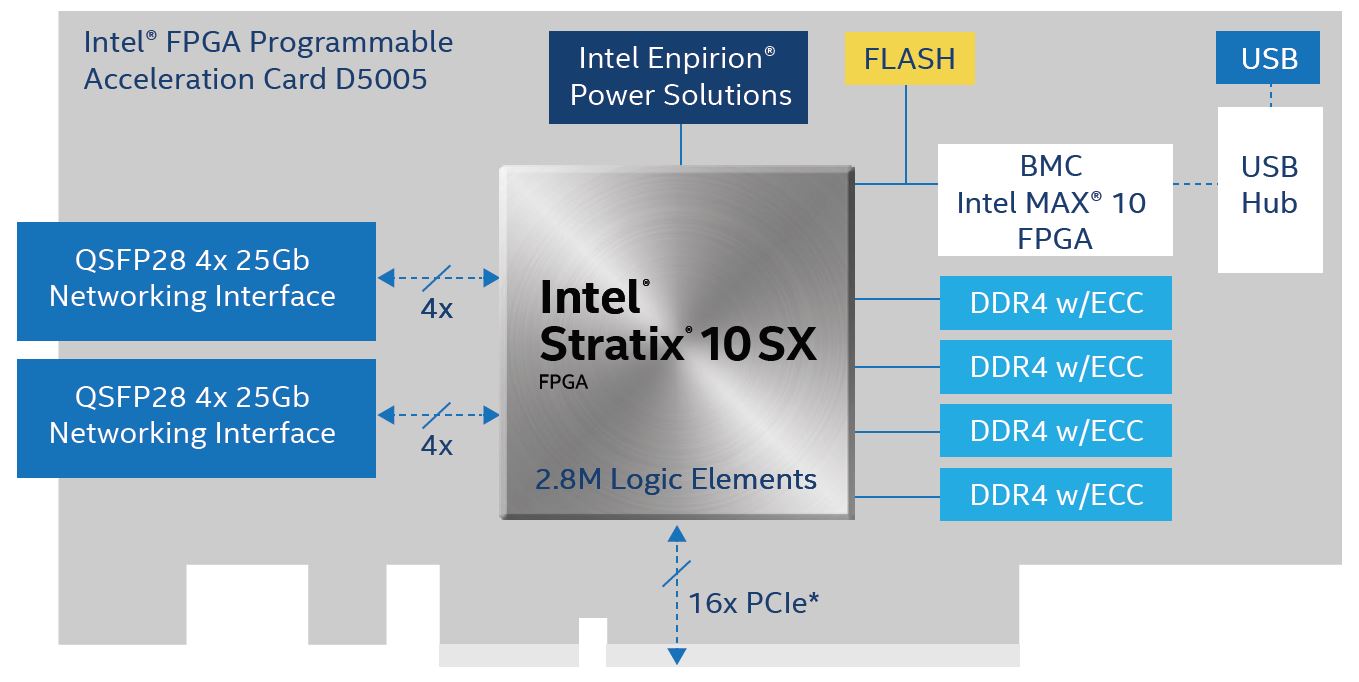

Intel FPGA PAC D5005 High-end Drop-in Accelerator: Here is yet another but general purpose FPGA Accelerator card can be used for

processing high-bandwidth Network and Storage Data Processing (hardware offload). Read the complete article

here.

Image courtesy/link: https://www.servethehome.com/wp-content/uploads/2019/08/Intel-FPGA-PAC-D5005-on-HPE-ProLiant-DL380-Gen10.jpg

Image courtesy/link: https://www.servethehome.com/wp-content/uploads/2019/08/Intel-FPGA-PAC-D5005-Diagram.jpg

References:

- AHA lossless data compression ICs

- Lossless Data Compression on GPUs

- AHA371/AHA372 PCI Express® Compression and Decompression Accelerator Card

Suggested Topics:

TOFFEE - WAN Optimization

Categories

| 💎 TOFFEE-MOCHA new bootable ISO: | Download |

| 💎 TOFFEE Data-Center Big picture and Overview: | Download PDF |

Saturday' 13-Mar-2021

Featured Educational Video:

Saturday' 13-Mar-2021

Saturday' 13-Mar-2021

Research :: Optimization of network data (WAN Optimization) at various levels:

Learn Linux Systems Software and Kernel Programming:

Hardware Compression and Decompression Accelerator Cards:

TOFFEE-DataCenter on a Dell Server - Intel Xeon E5645 CPU: